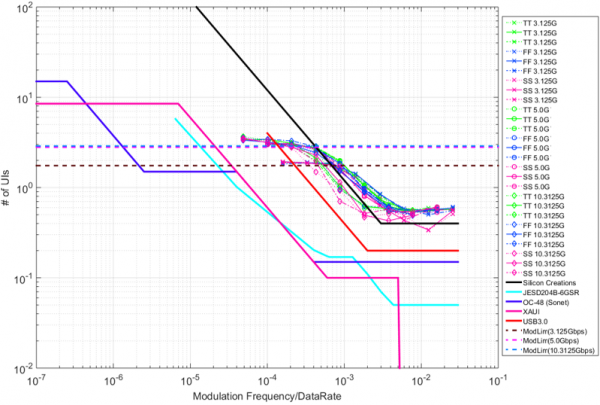

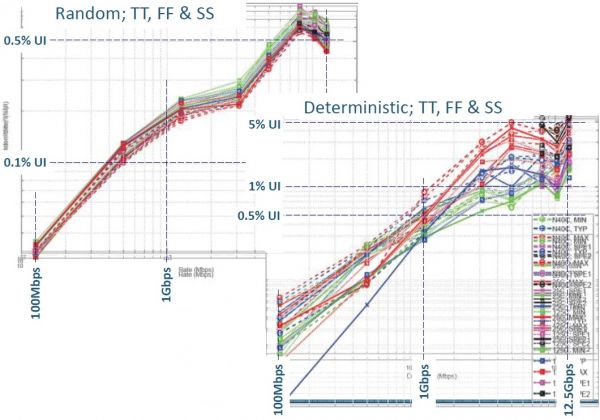

Our SerDes architecture is in production in processes ranging from 12nm to 180nm and at rates from 100Mbps to 32.75Gbps and proven in 6nm. We offer targeted PHYs including JESD204, XAUI, CPRI, SGMII, CPRI, OIF-CEI, V-by-One HS, Infiniband, PCIe1/2/3/4/5 and Serial RapidIO, and a Multiprotocol PMAs covering over 30 protocols from below 250Mbps to 32.75Gbps as well as SerDes designed for custom requirements. We partner with leading controller vendors to provide a complete solution, and can provide a complete PCIe PHY including PIPE PCS.

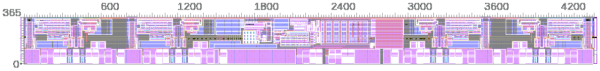

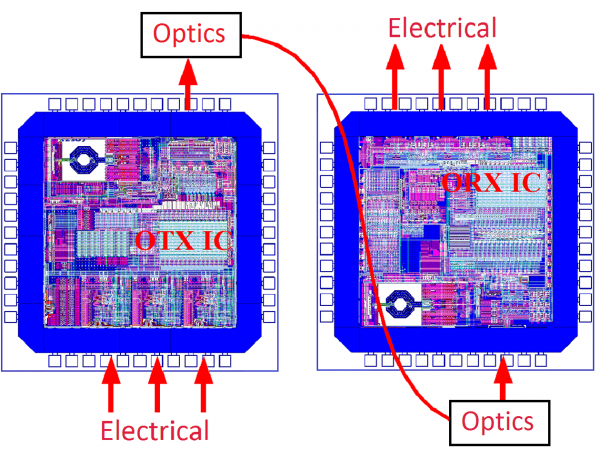

The examples shown on this page are a small subset of the successful SerDes we have built.

For more information on our SerDes Interfaces please download a product overview.

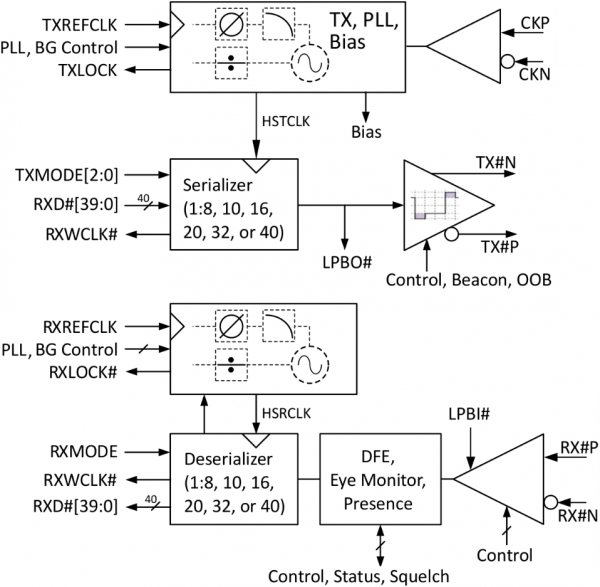

Simplified block diagram of Multiprotocol PMA. Features include:

- Supports over 30 protocols including CEI 6G & 11G SR, MR, LR, Ethernet 10GBASE-X/S/K/R, PCIe Gen1/2/3/4, V-by-One HS/US, CPRI, PON, OTN/OTU, 3GSDI, JESD204A/B/C, SATA1-3, XAUI, SGMII

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, or 40 bit

- Tx ring PLL includes fractional multiplication, spread spectrum and Jitter Cleaner function for Sync-E and OTU

- Core-voltage line driver with programmable pre-and post-emphasis

- Out-of-band, electrical idle signaling capability for SAS, SATA, and PCIe

- Ultra-low-Latency optimized PMAs with in-PMA latency below 13UI (<1.3ns at 10.3Gbps): See this overview.

- Burst mode CDR with tCDR < 150UI

- Programmable CTLE and adaptive 5-Tap Decision Feedback Equalizer for poor channels

- Non-destructive eye monitor to measure eye opening at data slicer on chip

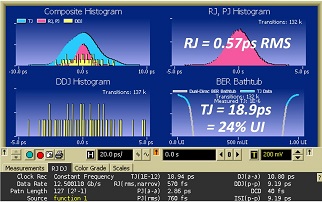

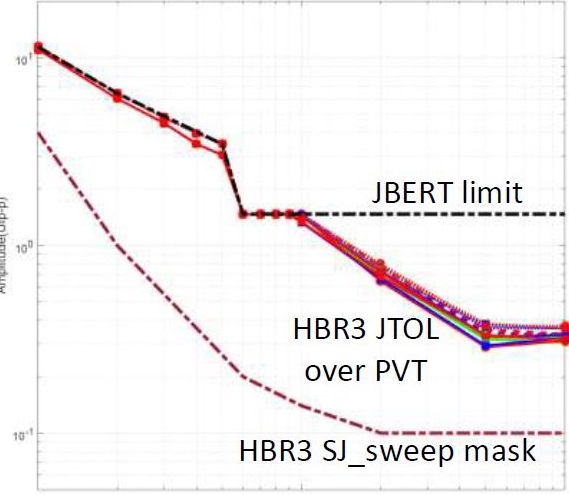

Excellent low jitter is stable over PVT using a ring PLL