General-purpose & Specialized Ring PLLs + RTL-based Solutions

Silicon Creations’ broad portfolio of general-purpose and optimized ring-based PLLs offer a wide range of clocking solutions. 500+ global customers rely on our proven IP and industry-leading support in over 750+ ICs fabricated on millions of wafers. Our PLL products are available in all major foundries and process nodes: Planar, FinFET and beyond.

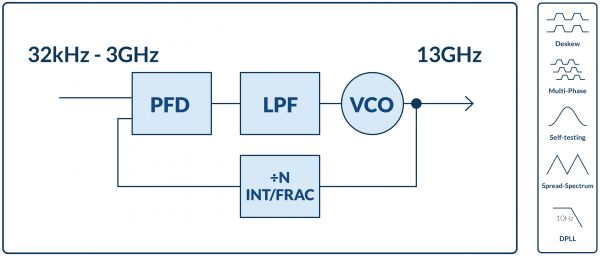

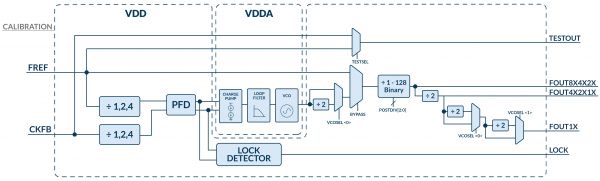

Figure 1: Generic PLL diagram with selected features and extensions

Silicon Creations engineers design robust PLL architectures as well as a number of supplementary circuits that can be used to design the clocking system for modern-day SoCs.

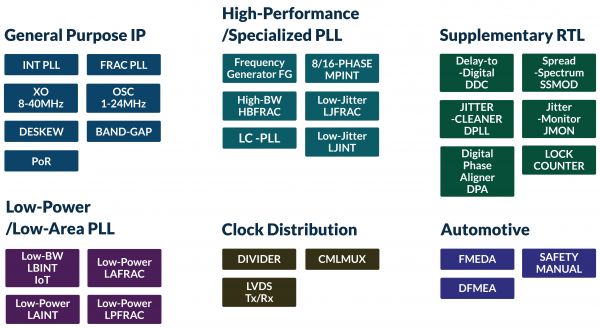

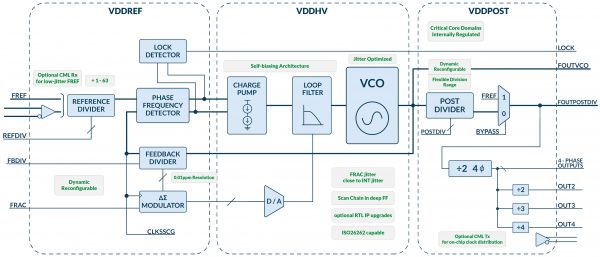

Figure 2: Silicon Creations product portfolio for SoC clocking

General-purpose PLLs:

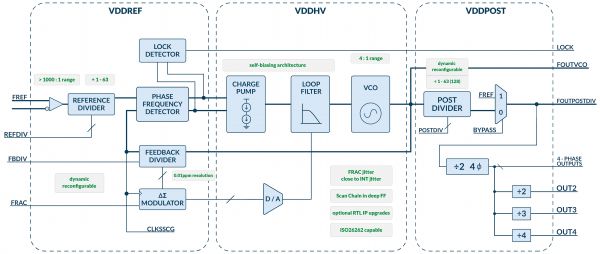

- Fractional-N PLL is a multi-function, general purpose frequency synthesizer. Ultra-wide input and output ranges along with excellent jitter performance, modest area, and application-appropriate power allow the PLL to be configured for almost any clocking application of complex SoC environments.

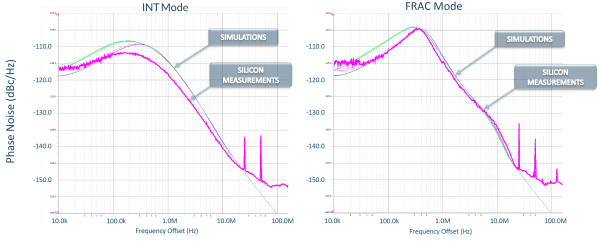

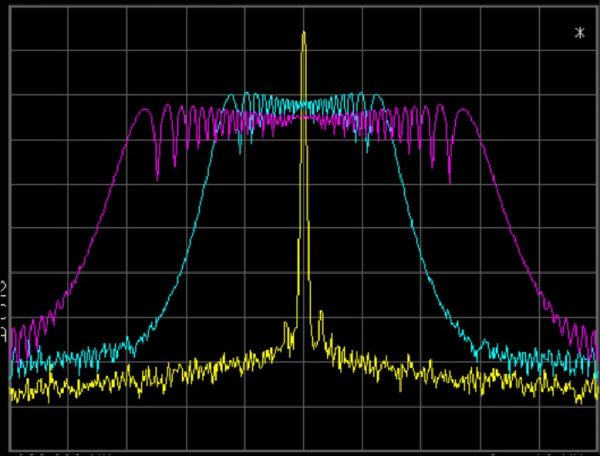

Figure 3/4: General-purpose Fractional-N PLL diagram with exemplary measurement vs simulated results

Optimized designs include:

- Low-Area Integer (or Low-Power) PLL that contains only crucial components and in some cases, no delta-sigma modulator. This PLL architecture lends itself to a high FoM with respect to period jitter while being roughly 4x smaller than general-purpose Fractional-N PLL.

- Low-Bandwidth PLL (IoT) is capable to operate with very low frequency reference (e.g. 32kHz) and achieve sub-mW power consumption. Provides VCO (and output) frequencies, on the order of tens or hundreds of MHz, enabling operation for many digital circuits.

- Low-Jitter PLL is the ultimate-performance ring-oscillator based circuit, achieving best-in-class sub-ps RMS long-term jitter and period jitter performance. Both Integer-N and Fractional-N modes are suitable for clocking precision data converters and SerDes, yet using a fraction of the die area needed for a traditional LC-PLL.

- For designs that call for the lowest possible jitter and higher oscillation frequencies, Silicon Creations’ LC-PLL circuits can be employed.

- Deskew PLL: Applicable for DDR interfaces and zero-delay buffer applications. Ability to work with high reference clock frequencies (e.g. 1600MHz), and can successfully track fast reference clock phase drift due to high loop bandwidth.

Figure 5/6: Generalized diagrams of De-skew PLL (top) and Jitter-Optimized (bottom) PLLs

- Multi-phase PLL provides from 4 up to 16 or even 32 outputs with accurately spaced phase suitable for phase alignment in source-synchronous data interfaces like DDR2, DDR3 and DDR4.

RTL-based Solutions:

- Spread-Spectrum Modulator RTL IP provides industry-standard and custom modulation patterns for Silicon Creations fractional-N PLLs.

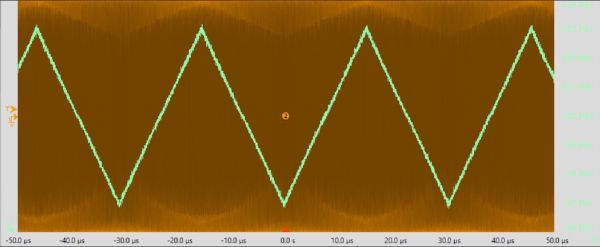

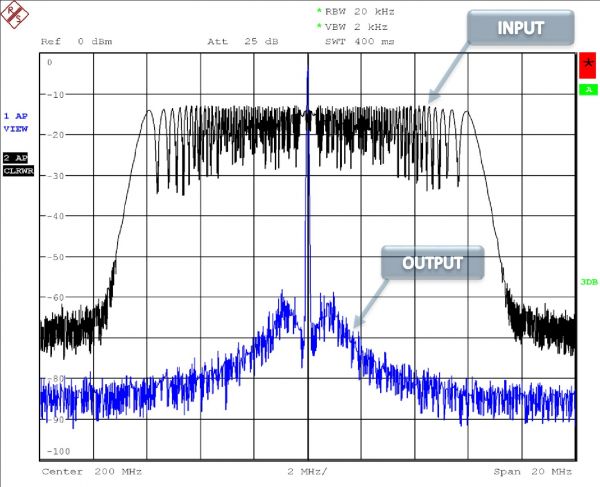

Figure 7/8: Exemplary waveforms of spread-spectrum clock generated with Silicon Creations PLL measured in frequency domain (top) and time-domain (bottom)

- Fully integrated Jitter Attenuator (Jitter Cleaner) RTL IP supplements PLLs to be used for Clock De-spreading, PON, OTU and Synchronous Ethernet applications with bandwidth programmable to below 1Hz.

Figure 9: Exemplary frequency domain measurements of spread-spectrum modulated reference clock and synthesized clock at the PLL output

- Jitter Monitor RTL IP allows on-chip clock jitter and duty cycle measurements.

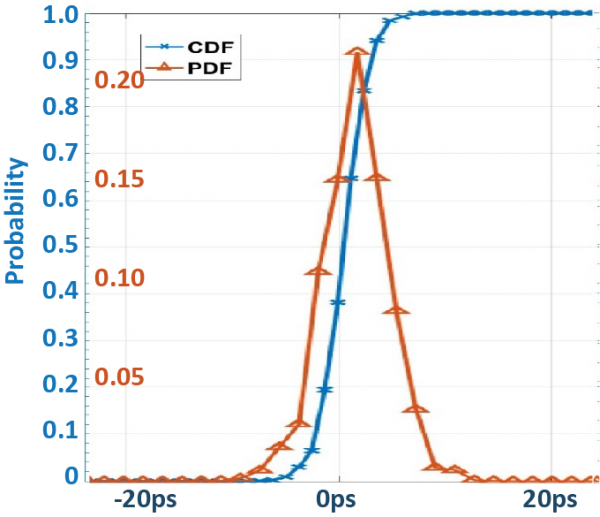

Figure 10: Exemplary jitter measurement result obtained with Jitter Monitor on-chip without any external measurement equipment.

- Digital Phase Aligner: An RTL IP that supplements the Fractional-N PLL to align clocks' phases and to track low-frequency phase variations.